Re: SP-Dif Spielerei für den Eclipse Sound Monitor

Das Teil ist mittlerweile bei mir angekommen.

Nun habe ich das etwas analysiert und Datenblätter gewälzt, bin aber ums verrecken nicht drauf gekommen, warum am SRC ne 27MHz clock verbaut ist und erst am Transmitter die 12.288MHz für die Ausgangssamplerate (48kHz Output) stecken.

An dieser Stelle vielen Dank an den Tom, der sich meiner Fragen angenommen hat und mir darüber hinaus auch einiges mehr zu der Schaltung erzählen konnte, als ich eigentlich gefragt hatte:

NT erzeugt zuerst 5V und daraus dann die 3,3V für alle ICs.

DC/DC Converter wäre auch vorgesehen, ist aber nicht bestückt.

Alle ICs arbeiten im Hardware Modus.

Der serielle Port vom Receiver (CS8416) ist im Master-Mode mit 128*Fs und im Port-Format I2S 24bit konfiguriert.

Via LRCK, SCLK, und DOUT geht es von dort in den SRC (SC8421). Dieser läuft von der digitalen Audio-Port-Konfiguration her (eingangs- wie auch ausgangseitig) im Slave-Mode.

D.h. die PINs 13 (OSCLK) und 14 (OLRCK) sind Eingänge und werden über den Output-Transmitter (CS8406) angesteuert (welcher dadurch die Ziel Sampling Rate dem Converter mitteilt).

Der 27.0000 MHz Quarz ist zwar mit den beiden Koppel-Cs und dem Serienwiderstand an den PINs: XTI, XTO angeschlossen .. hat hier aber keinen Einfluss auf die Ausgangssamplingrate. Theoretisch benötigt der SRC die 27MHz clock nur um lt. Datenblatt eine Sample Rate von 192kHz verarbeiten zu können (min. Fso/130, max 27Mhz), hat aber eigentlich keine direkte Funktion, da dies nur im Master Modus benötigt werden würde (wobei der hier ja mit SLV/SLV config läuft).

Das serielle Eingangsportformat ist logischerweise auf I2S (max. 32bit) festgelegt und das serielle "Ausgangs"-portformat auf I2S 24bit.

Der angeschlossene S/PDIF Transmitter (SC8406) läuft hier als Master und bekommt den Master-Clock PIN 21 (OMCK) von einem Quarz mit Single-Gate Schaltung (74HC04 in nem Tripple Gatter IC).

Per Hardware-Konfiguration ist der serielle Audio Eingang auf I2S gesetzt mit non-copyright im Datastream. Die Ausgangssamlingrate ist 256*Fs (bei 12.288MHz => 48kHz).

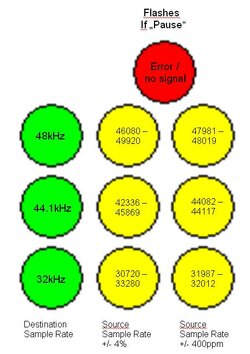

Demnach hat die clock am Transmitter direkten Einfluss auf die Sampling Rate. Nachdem da kein PLL Generator dazwischen steckt kann man einfach den Quarz tauschen und dann sollte der passende Output da sein.

Ergo: Quarz bestellt....